简单DDS(Direct Digital Synthesis,直接数字频率合成)系统

主要包含几个关键步骤:

- 相位累加器

- 相位幅度转换器(通常是一个查找表ROM)

- 数模转换器(DAC)

- 低通滤波器

相位累加器与DDS调谐公式

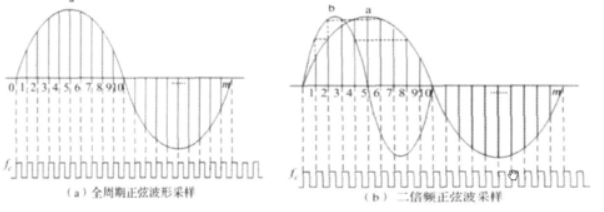

对一正弦波形进行采样,若每周期有m个采样点,分别记为1~m,即对应每次参考时钟fc来到上升沿就输出一个采样点,则输出如图中所示的一个周期的正弦,需要m个时钟周期,即需要m*1/fc的时间。

也即,输出的波形频率为fa=fc/m。

此时,每次时钟信号到来时,相位累加器加1,就会在第i个时钟周期输出第i个采样点(i=1~m),第m+1个时钟周期输出第1个采样点,以此循环。这时的相位累加器是步进为1的模m计数器。

若每次时钟信号到来时,总是间隔一个采样点输出,即相位累加器的步进2,这时在第i个时钟周期输出第2i个采样点,m’是m的0.5倍,故输出的波形频率为fa‘=2fa=2fc/m。

在实际设计中,相位累加器的单位是bits(位)。若相位累加器是N位(通常是24~48位)的,则有2N个存储单元来存储采样数据。如果我们队一个周期的波形进行2N个点的采样,即m=2N,此时输出频率fo、系统时钟频率fc、相位累加器长度N以及频率控制字B(即上文提到的,相位累加器的步进长度)的关系为:

此公式即为DDS调谐公式。

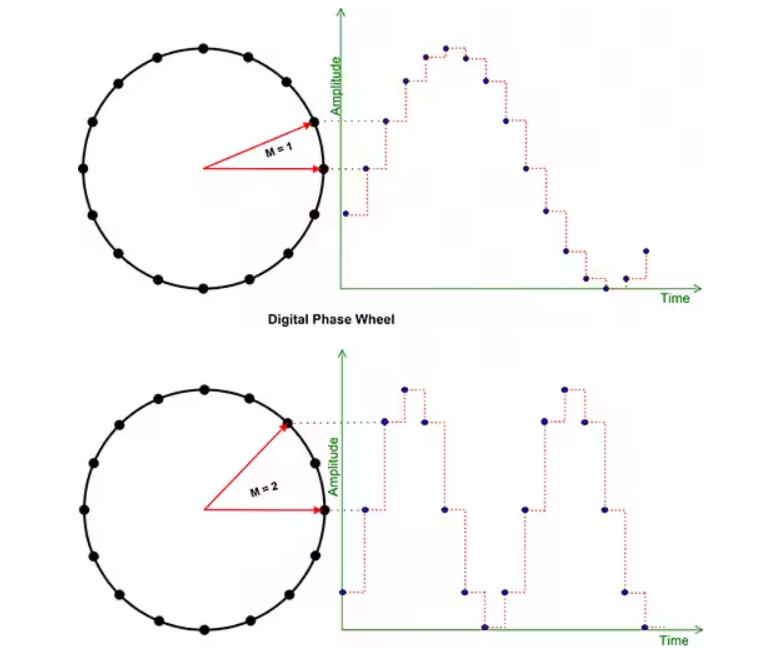

直观显示相位累加器运行情况的一种方法是,将累加器运行看作一个相位轮:

累加器状态具有周期性,显示为一个圆圈上的点。这些点表示累加器的各个相位状态。在本例中,为简单起见,假设累加器有 16 个状态。如上方的图所示,如果调谐字等于 1,那么每个时钟的步长增量均为 1,而且在整个周期内选中了所有状态。

相位轮的右侧显示的是每个状态的模拟输出。由于这是一个量化器件,因此模拟输出将保持其当前状态,直到时钟将相位轮推进到下一个状态。输出波形由包含 16 个值的单个量化正弦波周期组成。

在下方的图中,调谐字的值设置为 2。这时的相位轮上每隔一个状态被选中。对应的模拟输出由两个周期组成,每个周期有 8 个幅值,因此总共有 16 个状态。由于调谐字设置为 2,因此输出频率现在是之前所获值的两倍。

DDS 的输出频率由调谐字的值设定,并且按调谐字的值成比例地增加。采样率在系统时钟速率下保持不变,而且输出采样之间的时间恒定。输出频率取决于调谐字增量,因此随着调谐字的值增大,每个输出周期中的步长数会减少,从而增加了频率。调谐字可以增大到每个周期只有两个采样点,从而使 DDS 输出达到其奈奎斯特频率,即系统时钟速率的一半。通常,DDS 在设计上限制为输出频率总是小于奈奎斯特极限值。

采样与量化

奈奎斯特采样定理:采样率fs必须大于被测信号最高频率分量的两倍。

为了使波形输出不失真,利用DDS调谐公式与奈奎斯特采样定理,可推出B最高为2N-1。除此之外,要提高DDS的精度,需要分母尽可能地大。即采样点的个数越多,最终的输出波形越接近实际波形。

然而,实际上我们无法提供这么多的存储空间,故而需要对采样点进行量化。

量化:就是把经过抽样得到的瞬时值将其幅度离散。即用一组规定的电平,把瞬时抽样值用最接近的电平值来表示;或指把输入信号幅度连续变化的范围分为有限个不重叠的子区间(量化级),每个子区间用该区间内一个确定数值表示,落入其内的输入信号将以该值输出,从而将连续输入信号变为具有有限个离散值电平的近似信号 。

若量化单位为K,则前K个采样点的值相同,为采样值1;第二组K个采样点的值为采样值2,以此类推。第i组的K个采样点的值为采样值i,一共需要m/K个存储单元来存储m/K个采样点。

杂散

其来源之一是相位累加器的相位舍位。

现有的频率控制主要采用二进制频率控制原理(由于FPGA采用二进制的数据处理机制,且波形存储器使用了二进制寻址方式),故通常情况下m与K均为二进制整数,如m=2N。这就要求对计算结果进行十进制近似取舍,造成了波形发生器的输出频率以及频率分辨率存在无法消除的误差。

相位幅度转换器

相位累加器的输出作为波形存储器(通常是一个ROM)的索引。

ROM(Read-Only Memory,只读存储器)查找表是数字合成器(如DDS,Direct Digital Synthesizer)中用于将相位信息转换为幅度信息的关键组件。以下是ROM查找表的详细解释和作用:

存储波形数据:ROM查找表预先存储了波形的离散样本点数据。这些数据通常是通过数学计算或测量得到的,用于生成所需的波形,如正弦波、方波或其他复杂波形。

相位到幅度的转换:在DDS中,相位累加器的输出值(相位值)被用作ROM的索引。通过这个索引,可以从ROM中查找对应的幅度值。例如,如果相位累加器的输出值对应于正弦波的某个相位点,ROM查找表就会提供该相位点对应的正弦波幅度值。

实现波形生成:通过这种方式,DDS可以生成所需的波形。相位累加器不断累加,每次累加的结果都用来从ROM中查找相应的幅度值,从而生成连续的波形。

提高效率和精度:使用ROM查找表可以避免复杂的数学计算,提高波形生成的效率和精度。相比于实时计算波形,ROM查找表可以更快地提供波形数据,减少计算延迟。

灵活性:ROM查找表可以根据需要存储不同类型的波形数据,使得DDS系统能够灵活地生成多种波形。例如,可以存储正弦波、方波、三角波等不同波形的样本点数据。

实现调制功能:ROM查找表还可以用于实现波形的调制功能。通过改变相位累加器的输出值或直接修改ROM中的数据,可以实现频率调制、相位调制和幅度调制等。

硬件实现:在实际硬件中,ROM查找表可以是单独的存储芯片,也可以是FPGA或其他数字电路中的一部分。通过硬件实现,ROM查找表可以提供快速的访问速度和稳定的性能。

总之,ROM查找表在DDS系统中起到了将相位信息转换为幅度信息的关键作用,是实现高效、高精度波形生成的基础。

从ROM中查找对应的幅度值。这个查找表预先存储了波形的离散样本点,相位累加器的输出值对应于这些样本点中的一个,从而实现了从相位到幅度的转换。

数模转换器

相位幅度转换器的输出会发送到数模转换器(DAC),并转换为模拟波形。

由于DAC的输入是一系列采样值,因此输出具有量化步长。这些步长在频域内以采样率的倍数产生频谱响应。

量化噪声:在DAC中,量化步长决定了数字信号的分辨率。每个量化级别对应一个特定的模拟电压。量化步长越小,表示的模拟电压越精细。量化噪声是由于信号在量化过程中不能精确表示而产生的误差。这种噪声在频域内表现为一个宽带噪声,其频率成分可以扩展到采样率的倍数。

频谱泄露:由于量化步长的存在,原始信号的某些频率成分可能无法被完美地表示。这会导致信号的频谱在采样率的整数倍处产生泄露,即信号的频谱在这些频率点上出现不期望的响应。这种现象称为频谱泄露,是量化步长在频域内产生响应的一种表现。

因此,需要后接一个低通滤波器来抑制这些不需要的频谱响应。

使用输出低通滤波器的原因

DAC输出波形由于其阶跃特性而富含谐波。因此,必须使用低通滤波器来消除这些频谱谐波,以及 DDS 中其他工艺产生的其他杂散频率响应。

例如,下图显示了一个器件在时钟频率为 fc、输出频率小于 fc/2 时的 DDS 输出频谱。该输出频谱显示了输出频谱线 fout,及其高于和低于时钟频率的镜像频率,还有高达和超过第三次谐波的所有谐波。

DDS 输出频率范围为 0 Hz 到奈奎斯特极限 fc/2。sin(x)/x 整形是由于时域中的量化信号而引起,如图所示。sin(x)/x 函数的零值发生在时钟频率及其所有谐波处。要在输出范围内提高幅度平坦度,可通过幅值校正来取消 sin(x)/x 整形。

为了显著减小超过奈奎斯特频率的频谱成分幅度,采用了具有高于 DDS 频率范围的锐截止特性的低通滤波器。如果将 DDS 频率范围扩展到奈奎斯特频率,则滤波器需要无限陡的截止斜率,以便排除时钟频率的低镜像频率,否则会与奈奎斯特频率重叠。这也是 DDS 频率范围很少扩展到奈奎斯特频率的一个原因。

AD9834

元件基础介绍

AD9834是一个集成的DDS系统。

AD9834是一款75 MHz、低功耗DDS器件,能够产生高性能正弦波和三角波输出。其片内还集成一个比较器,支持产生方波以用于时钟发生。当供电电压为3 V时,其功耗仅为20 mW,非常适合对功耗要求严格的应用。

AD9834提供相位调制和频率调制功能。频率寄存器为28位;时钟速率为75 MHz,可以实现0.28 Hz的分辨率。同样,时钟速率为1 MHz时, AD9834可以实现0.004 Hz的分辨率。影响频率和相位调制的方法是通过串行接口加载寄存器,然后通过软件或FSELECT/PSELECT引脚切换寄存器。

AD9834通过一个三线式串行接口写入数据。该串行接口能够以最高40 MHz的时钟速率工作,并且与DSP和微控制器标准兼容。

该器件采用2.3 V至5.5 V电源供电。模拟和数字部分彼此独立,可以采用不同的电源供电;例如, AVDD可以是5 V,而DVDD可以是3 V。

AD9834具有控制休眠的引脚(SLEEP),支持从外部控制断电模式。器件中不用的部分可以断电,以将功耗降至最低。例如,在产生时钟输出时,可以关断DAC。

该器件采用20引脚TSSOP封装。

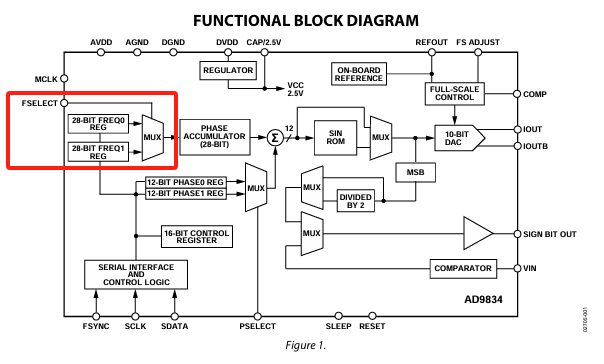

功能框图

数据手册所示功能框图如下,红圈部分即是上文所述的,需要利用软件切换的寄存器之一。

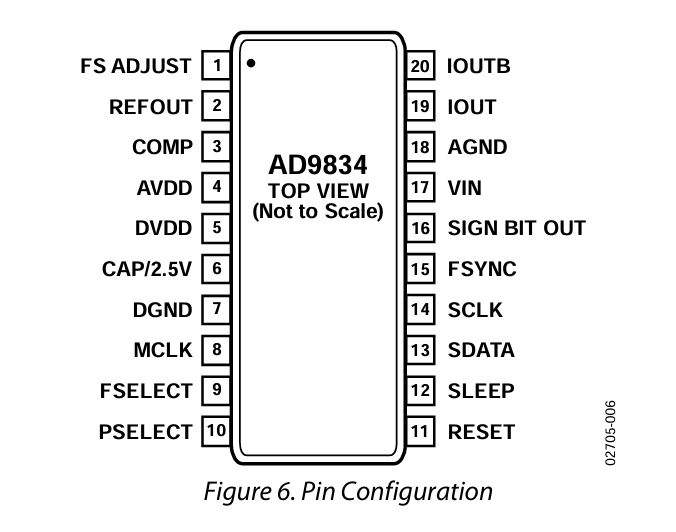

引脚设置

引脚如下:

各引脚功能如下:

模拟信号和基准电压源

| 引脚编号 | 引脚名称 | 描述 |

|---|---|---|

| 1 | FS ADJUST | 满量程调整控制。此引脚和AGND之间连接一个电阻(RSET),从而决定满量程DAC电流的幅度。RSET与满量程电流之间的关系如下:IOUTFULL SCALE = 18 × FS ADJUST/RSET【FS ADJUST = 1.15 V(标称值), RSET = 6.8 kΩ(典型值)】 |

| 2 | REFOUT | 基准电压输出。AD9834通过此引脚提供1.20V内部基准电压源。 |

| 3 | COMP | DAC偏置引脚。此引脚用于对DAC偏置电压进行去耦。 |

| 17 | VIN | 比较器输入。可利用比较器从正弦DAC输出产生方波。DAC输出应经过适当滤波,然后再施加于比较器,以改善抖动性能。当控制寄存器中的Bit OPBITEN和Bit SIGN/PIB置1时,比较器输入端连接到VIN。 |

| 19,20 | IOUT,IOUTB | 电流输出。这是高阻抗电流源。应在IOUT和AGND之间连接一个标称值为200 Ω的负载电阻。IOUTB最好应通过一个大小为200 Ω的外部负载电阻连接到AGND,但也可直接与AGND相连。此外还建议通过一个20 pF电容连接到AGND,以防出现时钟馈通。 |

时钟馈通(Clock Feedthrough)是一种在数字电路中常见的问题,特别是在高速数字电路设计中。它通常发生在时钟信号的路径上,由于高速信号的快速切换,可能会产生一些不希望的信号传输或干扰。

电源

| 引脚编号 | 引脚名称 | 描述 |

|---|---|---|

| 4 | AVDD | 模拟部分的正电源,范围是2.3V~5.5V。应在AVDD与AGND之间连接一个0.1μF去耦电容。 |

| 5 | DVDD | 数字部分的正电源,范围是2.3V~5.5V。应在DVDD与DGND之间连接一个0.1μF去耦电容。 |

| 6 | CAP/2.5V | 数字电路采用2.5V电源供电。当DVDD超过2.7 V时,此2.5 V利用片内调节器从DVDD产生,该调节器需要在CAP/2.5V至DGND之间连接一个典型值为100 nF的去耦电容;如果DVDD小于或等于2.7 V,则CAP/2.5 V应与DVDD直接相连。 |

| 7 | DGND | 数字地。 |

| 18 | AGND | 模拟地。 |

数字接口和控制

| 引脚编号 | 引脚名称 | 描述 |

|---|---|---|

| 8 | MCLK | 数字时钟输入。 DDS输出频率是MCLK频率的一个分数,分数的分子是二进制数。输出频率精度和相位噪声均由此时钟决定。 |

| 9 | FSELECT | 频率选择输入。 FSELECT控制相位累加器中使用的具体频率寄存器(FREQ0或FREQ1)。可使用引脚FSELECT或Bit FSEL来选择要使用的频率寄存器。使用Bit FSEL来选择频率寄存器时, FSELECT引脚应与CMOS高电平或低电平相连。 |

| 10 | PSELECT | 相位选择输入。 PSELECT控制将增加到相位累加器输出的具体相位寄存器(PHASE0或PHASE1)。可使用引脚PSELECT或Bit PSEL来选择要使用的相位寄存器。当相位寄存器由Bit PSEL控制时, PSELECT引脚应与CMOS高电平或低电平相连。 |

| 11 | RESET | 高电平有效数字输入。RESET可使相应的内部寄存器复位至0,以提供中间电平的模拟输出。 RESET不影响任何可寻址寄存器。 |

| 12 | SLEEP | 高电平有效数字输入。当此引脚处于高电平时, DAC关断。此引脚功能与控制位SLEEP12相同。 |

| 13 | SDATA | 串行数据输入。 16位串行数据字施加于此输入。 |

| 14 | SCLK | 串行时钟输入。数据在每个SCLK下降沿逐个输入。 |

| 15 | FSYNC | 低电平有效控制输入。这是输入数据的帧同步信号。当FSYNC变为低电平时,即告知内部逻辑,正在向器件中载入新数据字。 |

| 16 | SIGN BIT OUT | 逻辑输出。比较器输出通过此引脚提供,或者可通过此引脚输出NCO的MSB。通过将控制寄存器中的Bit OPBITEN置1,可使能此输出引脚。 Bit SIGN/PIB确定通过该引脚输出的是比较器输出还是NCO(数控振荡器,用以生成特定频率与相位的正弦波)的MSB。 |

工作原理

在简单DDS系统的基础上,AD9834的内部电路包含:数控振荡器(NCO)、频率调制器、相位调制器、SIN ROM、DAC、比较器以及稳压器。

数控振荡器和相位调制器

该子电路由两个频率选择寄存器、一个相位累加器、两个相位偏移寄存器和一个相位偏移加法器组成。 NCO的主要元件是一个28位相位累加器。连续时间信号的相位范围为0 π至2 π。在此数值范围之外,正弦函数以周期方式不断重复。

因此,在AD9834中, 2π = 228。同样, ΔPhase项也会扩大至此数值范围:0 < ∆Phase < 228− 1

将这些带入前面的公式可得:

fo = ∆Phase × fMCLK/228

其中, 0 < ∆Phase < 228 − 1.

相位累加器的输入可以从FREQ0寄存器或FREQ1寄存器进行选择并由FSELECT引脚或FSEL bit控制。 NCO本身会产生连续相位信号,因此在频率之间切换时应避免出现任何输出不连续。

在NCO之后,可以使用12位相位寄存器添加一个相位偏移来执行相位调制。这些相位寄存器之一的内容会增加到NCO的MSB。 AD9834具有两个相位寄存器,且这两个寄存器的分辨率均为2π/212。

SIN ROM

要使用NCO的输出,必须先将其从相位信息转换成正弦数值。相位信息可以直接映射至幅度,因此SIN ROM可以将数字相位信息用作查找表的地址,并将相位信息转换成幅度。

虽然NCO包含28位相位累加器,但NCO的输出会被截断至12位。使用相位累加器的全分辨率不仅不切实际,也根本不必要,因为这要求查找表具有228个条目。只需具有足够的相位分辨率,使得因截断而产生的误差小于10位DAC的分辨率。这就要求SIN ROM的相位分辨率比10位DAC高出两位。

可使用控制寄存器中的OPBITEN和MODE bits来使能SIN ROM。

用AD9834实现信号调制

AM调制(调幅)

—参考资料:cn0156_cn.pdf (analog.com)

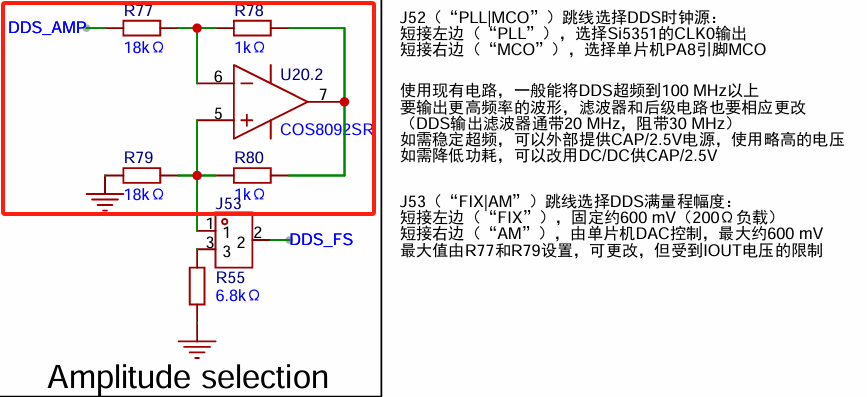

由引脚介绍可知,AD9834的FS ADJUST引脚(标称值,FS ADJUST = 1.15 V)是模拟输入端口,接受电流,用于控制满量程DAC输出电流的幅度,其一般做法是改变RSET的值,其标准值是6.8kΩ。

但也可以用一个外围电路来调制AD9834的幅度输出,ADI官网有一份技术文档,使用的是可调的外围DAC电路:

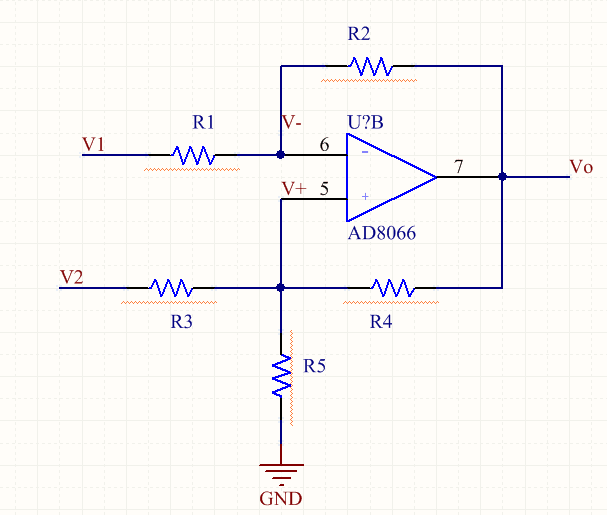

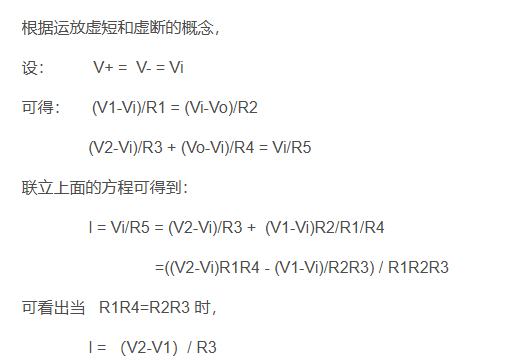

参赛板上的外围电路如图所示,是霍兰德电流源:

其中DDS_AMP接在单片机的DAC输出引脚上。

—参考资料:howland电流源公式推导-CSDN博客

则霍兰德电流源的电流输出为:

又由大板的电路图知:V2=DDS_AMP(接单片机PA6,DAC输出),V1=GND=0,R79=18kΩ。

故有:

其中V2即为单片机的DAC输出。

FSK调制(频率键控)

FSK是通过改变载波的频率来传输信息的一种调制方式。使用AD9834实现FSK的步骤如下:

- 设置两个频率:在AD9834中设置两个不同的频率寄存器,分别对应二进制”1”和”0”。

- 频率切换:根据要传输的数据,使用频率选择引脚或控制位在两个频率寄存器之间切换。

PSK调制(相位键控)

PSK是通过改变载波的相位来传输信息的一种调制方式。使用AD9834实现PSK的步骤如下:

- 设置频率:首先,设置AD9834的频率寄存器,以确定载波的基本频率。

- 相位调制:使用AD9834的相位调制功能,根据要传输的数据改变相位累加器的初始相位值。例如,数据”1”可以对应相位累加器增加一个特定的相位偏移,而数据”0”则不增加偏移。

Author: MosiS